For the first time at true hyperscale, a social platform’s AI backbone is being rebuilt around commodity-efficient Arm CPUs to orchestrate billions of agentic interactions while GPUs and custom accelerators focus on raw parallel compute. Meta’s agreement to deploy tens of millions of AWS Graviton5 cores is not a retreat from accelerators; it is a bet that persistent, stateful AI services demand a different kind of engine for the control plane. The move reframes CPUs as coordination hubs for long-lived agents, task graphs, retries, and memory-bound services, and it recasts success metrics from peak FLOPS to sustained efficiency and total cost of ownership.

What matters is how this architecture changes the economics and behavior of AI at scale. Training remains a GPU-first domain, but production AI is turning into a mesh of services that never sleep: vector stores, caches, policy evaluators, schedulers, and safety rails driving real-time decisions. Graviton5, with its 192-core design and AWS Nitro isolation, slots in as the consistent, power-thrifty substrate for that fabric. The question is whether this composable, heterogeneous stack can outpace single-vendor designs in performance, reliability, and supply resilience without drowning teams in complexity.

Deep Dive: Architecture, Performance, and Fit

Graviton5’s value starts with first principles: many lean Arm cores, consistent memory bandwidth, and the Nitro System offloading virtualization, networking, and storage I/O into dedicated hardware. That separation shrinks noisy-neighbor effects and stabilizes tail latency, which is essential for orchestrators that must keep accelerator pipelines fed and responsive. In practice, these CPUs are not there to out-crunch GPUs; they are there to keep the whole machine synchronized, recover from partial failures, and adjudicate workload placement with millisecond awareness of queue depth and policy.

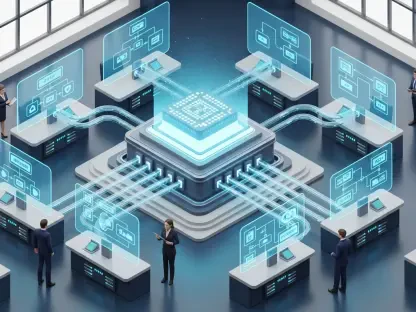

Agentic AI lifts CPUs from supporting cast to command center. Multi-stage workflows—prefill on a GPU cluster, decode on a different slice, retrieval against a vector index, policy checks, and post-processing—benefit when a deterministic control plane can reason about state and time. Arm’s energy profile helps here: a “little work, always on” pattern maps to orchestration loops, token accounting, and session continuity. The distinctive bit is the sustained duty cycle; these services run continuously, so watts per unit of useful coordination matter more than theoretical peaks.

Integration with accelerators exposes the sharper edge. Nvidia still leads training, bolstered by Spectrum-X Ethernet for east-west traffic and tight software stacks. AMD brings optionality across CPUs and AI accelerators with credible performance per dollar, plus meaningful power envelopes that fit dense deployments. Meta’s MTIA adds targeted paths for inference and training variants, shortening the design loop for bottlenecked operators. In this division of labor, Graviton5 becomes the glue: dispatching, batching, shaping microservice calls, and deciding when to split prefill from decode to balance latency against utilization.

Performance must be read as throughput per watt and stability under load, not stand-alone SPEC numbers. A Graviton5 control tier reduces accelerator idle time by improving admission control and coalescing small requests, which in turn raises effective GPU occupancy. That synergy is the real metric: if the CPU tier trims p95 and p99 tails and prevents batching collapse, total cost of serving drops even when raw GPU minutes stay constant. Compared with x86, Arm here leans on better performance per watt for steady-state tasks and often lower instance pricing, but trade-offs include porting costs, nuanced compiler behavior, and mixed third-party library maturity.

Ecosystem dynamics amplify the rationale. Access to Nvidia’s Blackwell/Rubin cadence remains precious and contentious; supplementing with vast CPU capacity hedges capacity risk. AMD’s up-to-6GW path adds scale diversity. Arm and custom silicon sustain architectural control and faster iteration on specific kernels. The common thread is supply diversity as strategy: rather than chase one perfect chip, the stack assigns each job to the resource that clears it fastest and cheapest within SLOs. That workload-aware placement is the new procurement logic.

Real deployments sharpen the picture. Orchestration tiers handle dependency resolution, retries, and policy enforcement; stateful services hold memory graphs, features, and session state for agentic loops; runtime managers partition inference, pushing prefill toward larger, high-bandwidth GPU pools while steering decode and light adapters to where batching throughput holds. Site reliability teams then watch cross-silicon health, enforce admission budgets, and quarantine noisy neighbors using Nitro-backed isolation to keep blast radius small. The result is less glamorous than a new GPU, but it is what keeps the model’s answers on time.

Still, there are frictions. Cross-architecture toolchains and debuggers lag, and observability across CPUs, GPUs, and custom accelerators remains uneven—especially for memory coherence and queuing backpressure. Scheduling heuristics must juggle data locality against utilization, often with incomplete signals. Supply-chain choreography across multiple vendors complicates capacity planning, and network topology can bottleneck the very elasticity that heterogeneous designs promise. Governance adds yet another layer: data residency and safety guardrails for agents demand explainability in a distributed, multi-tenant fabric.

The strategic upside is tangible. A stable, efficient CPU substrate lets teams iterate on agent behaviors without burning expensive accelerator hours, and it unlocks persistent services that can later be selectively exposed—think Llama APIs with integrated retrieval, tools, and policies. The economics shift to end-to-end efficiency: latency SLOs, p99 reliability, and power-bounded throughput decide wins and losses. The differentiator versus competitors is not any single chip, but how tightly the chips are choreographed and how quickly capacity can pivot as models and workloads change.

Conclusion: Verdict and What Comes Next

This expansion read as an additive, hedged bet that elevated CPUs to first-class citizens in agentic AI, not a pivot away from accelerators. The distinctive advantage lay in pairing Graviton5’s efficiency and Nitro-backed isolation with a portfolio of GPUs and custom silicon, then optimizing for sustained, latency-sensitive coordination rather than headline throughput. The trade-offs—tooling gaps, integration complexity, and planning across multiple vendors—were real but manageable when balanced against supply resilience and lower steady-state costs.

The verdict: for organizations running persistent AI services, a Graviton5-like control plane made architectural and economic sense, provided teams invested early in cross-architecture build systems, observability, and policy-aware schedulers. The next step should have been formal workload partitioning—prefill versus decode, stateless versus stateful—codified as platform contracts, followed by targeted accelerator pairing and power-aware admission control. Over time, expect tighter CPU–accelerator co-packaging, richer programmable fabrics, and selective external exposure of agentic stacks with built-in guardrails. Those willing to design for heterogeneity gained leverage not just over performance, but over time-to-capacity in a market where supply, not aspiration, set the pace.